Exercise: Counters

Questions for: Counters

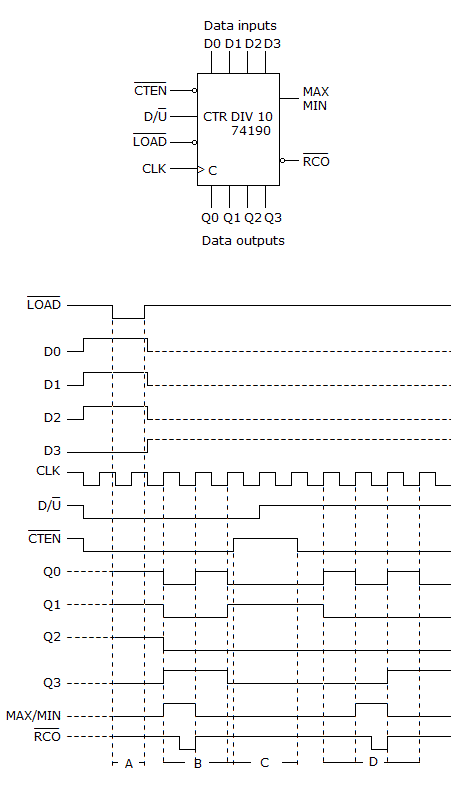

What function will the counter shown below be performing during period "B" on the timing diagram?

A:

Counting up

B:

Counting down

C:

Inhibited

D:

Loading

Answer: A

No answer description is available. Let's discuss.

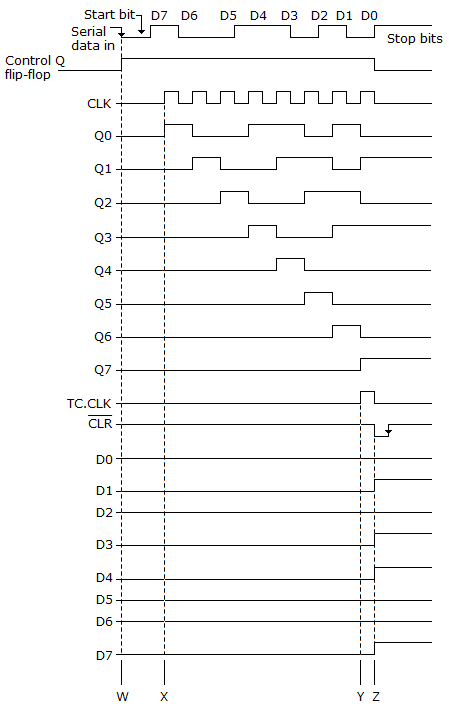

Referring to the given figure, what causes the Control FF to reset after D7?

A:

Once the data cycle is initiated by the Start bit, the one-shot produces an output pulse equal to the duration of the eight data bits. Once the eight data bits have been transferred to the data input register, the falling edge of the one-shot pulse resets the Control FF to start the sequence all over again.

B:

After counting the eight data bits, the divide-by-8 counter produces an output on its active-LOW CLR line to reset the Control FF.

C:

After counting eight clock pulses equivalent to eight data periods, the terminal count of the divide-by-8 counter and the clock trigger the one-shot, which in turn resets the Control FF and divide-by-8 circuits to begin the sequence all over again. Simultaneously the data is transferred through the output register.

D:

When the data output register is full, it produces an output on its C terminal that triggers the one-shot, which in turn resets the Control FF.

Answer: C

No answer description is available. Let's discuss.

Discuss About this Question.

List the state of each output pin of a 7447 if RBI = 0, LT = 1, A0 = 1, A1 = 0, A2 = 0, and A3 = 1.

A:

RBO = 0, a = 0, b = 0, c = 0, d = 1, e = 1, f = 0, g = 0

B:

RBO = 1, a = 0, b = 0, c = 0, d = 1, e = 1, f = 0, g = 0

C:

RBO = 0, a = 0, b = 0, c = 0, d = 0, e = 1, f = 0, g = 0

D:

RBO = 1, a = 0, b = 0, c = 0, d = 0, e = 1, f = 0, g = 0

Answer: A

No answer description is available. Let's discuss.

Discuss About this Question.

Synchronous (parallel) counters eliminate the delay problems encountered with asynchronous (ripple) counters because the:

A:

input clock pulses are applied only to the first and last stages.

B:

input clock pulses are applied only to the last stage.

C:

input clock pulses are applied simultaneously to each stage.

D:

input clock pulses are not used to activate any of the counter stages.

Answer: C

No answer description is available. Let's discuss.

Discuss About this Question.

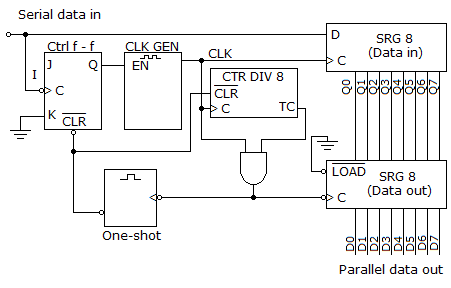

What function does the CTR DIV 8 circuit given below perform?

A:

It divides the clock frequency down to match the frequency of the serial data in.

B:

The divide-by-8 counter is triggered by the control flip-flop and clock, which then allows the data output register to begin storing the input data. Once all eight data bits are stored in the data output register, the data output register and the divide-by-8 counter trigger the one-shot. The one-shot then begins the process all over again.

C:

The divide-by-8 counter is used to verify that the parity bit is attached to the input data string.

D:

It keeps track of the eight data bits, triggering the transfer of the data through the output register and the one-shot, which then resets the control flip-flop and divide-by-8 counter.

Answer: D

No answer description is available. Let's discuss.

Discuss About this Question.

Ad Slot (Above Pagination)

Discuss About this Question.